新闻资讯

新闻资讯

- 智能药盒中的霍尔元件应用:优选无锡迪仕科技全极低功耗霍尔元件DH629

- 霍尔元件在汽车电子中的关键应用与技术解析

- 国产替代纵深战:霍尔元件,何以成为工业控制的“隐形冠军”?

- KMXP2000/KMXP5000替代方案:迪仕科技VCP1612/VCP1615

- 一文了解场效应管的作用和用法

联系我们

手机:18961874527

电话:17605104520

邮箱:wh@deestech.com

地址:无锡市锡山区索立得国际科技园9号楼3楼

行业新闻

霍尔元件PCB布局的10个防干扰技巧

- 作者:无锡迪仕科技

- 发布时间:2025-07-07

- 点击:1074

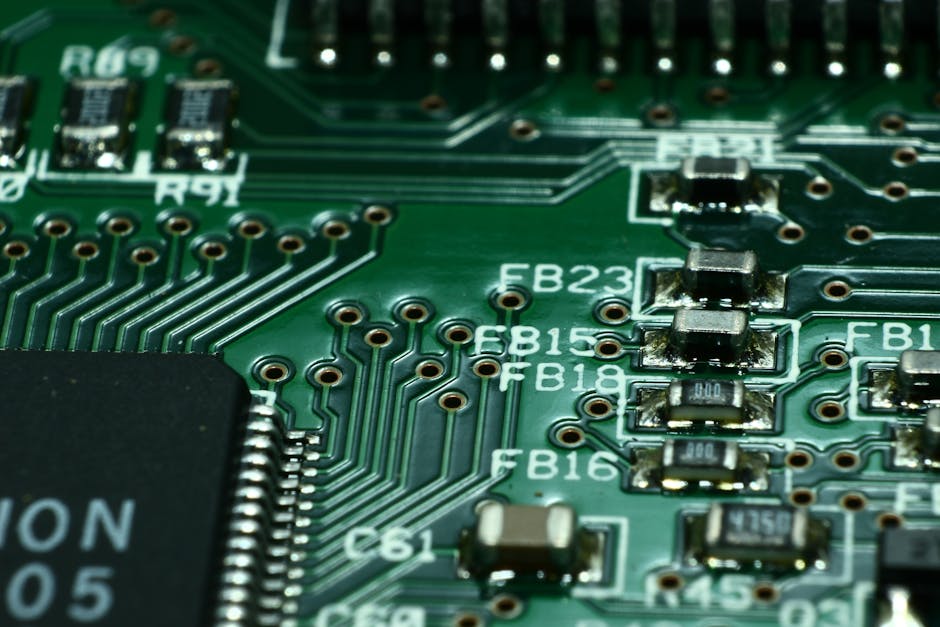

在霍尔元件的PCB布局中,为有效防止干扰,需结合磁场特性、信号完整性及电磁兼容性设计,以下是10个关键防干扰技巧:

定向高电流导体垂直布局

将高电流导体(如电源线、电机驱动线)定向为垂直于霍尔元件平面的方向。此时磁通量在元件平面内循环,而非垂直穿过元件,可显著降低外部磁场对霍尔元件的干扰。例如,在电机控制电路中,将电源线与霍尔传感器平面呈90°布局,可减少电机磁场对传感器输出的影响。保持元件与载流走线安全间距

在空间受限的PCB中,需在霍尔元件与其他载流走线(如高速信号线、高频开关线)之间保留尽可能大的间距。一般建议间距不小于线宽的3倍,以减少互感和电容耦合效应。例如,若信号线宽为0.2mm,则霍尔元件与其间距应至少为0.6mm。采用表面贴装磁屏蔽覆盖封装

使用表面贴装磁屏蔽(如铁氧体材料)覆盖霍尔元件封装,可将外部杂散磁场从封装中分流出去,同时不影响元件内部载流路径产生的磁场。屏蔽层需通过环氧树脂固定在PCB上,并确保屏蔽两侧开放(因霍尔元件对平行于平面的磁通线不敏感)。双层屏蔽设计(垂直磁场防护)

若电路需额外屏蔽外部垂直磁通,可在PCB底部放置第二层屏蔽。例如,在汽车轮速传感器应用中,双层屏蔽可有效抑制车轮旋转产生的动态磁场干扰,确保霍尔元件输出稳定性。模拟/数字电路分区布局

将霍尔元件的模拟信号处理电路(如放大器、滤波器)与数字电路(如微控制器、通信接口)分区布局,并在两区域间设置隔离带或使用光电耦合器、磁珠等隔离元件。例如,在电机控制系统中,将霍尔传感器信号调理电路与PWM驱动电路分开布局,可减少数字噪声对模拟信号的干扰。构建完整地平面

为霍尔元件信号提供低阻抗返回路径,需构建完整的地平面(如多层板中的内电层或双面板中的大面积铺铜)。避免地线断裂或分隔,确保存在多个接地路径,以减少地环路电流和信号失真。例如,在四层板设计中,将霍尔元件所在层紧邻地平面,可显著降低地线阻抗。差分信号线设计

对霍尔元件输出的差分信号(如某些高精度电流传感器),采用同层、等长、并行走线,并保持差分线间无其他走线。此设计可保证差分线对共模阻抗相等,提高抗干扰能力。例如,在电力监测系统中,差分信号线布局可有效抑制共模噪声。关键信号线3W原则布局

霍尔元件的时钟线、总线等关键信号线与其他同层平行走线需满足3W原则(线间距不小于线宽的3倍),以避免信号间串扰。例如,若信号线宽为0.1mm,则与其他线间距应至少为0.3mm。敏感信号线远离干扰源

将霍尔元件的复位信号、片选信号等敏感信号线远离接口外出信号线(如UART、CAN总线),避免外来干扰耦合导致系统误操作。例如,在工业自动化控制系统中,敏感信号线与通信线间距应大于2mm。滤波电容就近布局

为霍尔元件供电的滤波电容(如0.1μF陶瓷电容)需尽可能靠近芯片的供电管脚放置,以减小高频回路面积和辐射。例如,在电池供电的便携设备中,滤波电容与霍尔元件引脚间距应小于0.5mm,可有效抑制电源噪声。

- 上一篇:PCB设计中过孔为什么要错开焊盘位置?

- 下一篇:识别优质霍尔元件的5个关键参数

苏公网安备32021302001985

苏公网安备32021302001985

客服QQ

客服QQ